### Single-Channel Monochrome On-Screen Display with Integrated EEPROM

#### **General Description**

The MAX7456 single-channel monochrome on-screen display (OSD) generator lowers system cost by eliminating the need for an external video driver, sync separator, video switch, and EEPROM. The MAX7456 serves all national and international markets with 256 user-programmable characters in NTSC and PAL standards. The MAX7456 easily displays information such as company logo, custom graphics, time, and date with arbitrary characters and sizes. The MAX7456 is preloaded with 256 characters and pictographs and can be reprogrammed in-circuit using the SPI<sup>TM</sup> port.

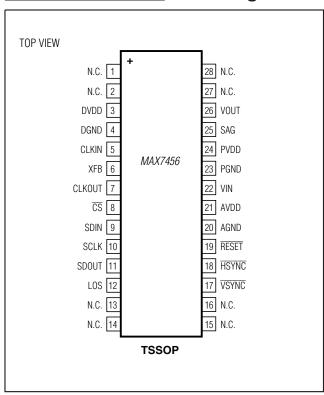

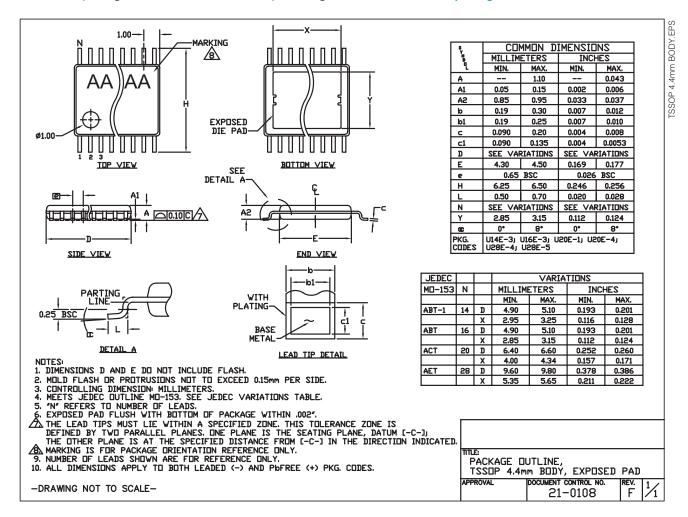

The MAX7456 is available in a 28-pin TSSOP package and is fully specified over the extended (-40°C to +85°C) temperature range.

#### **Applications**

Security Switching Systems Security Cameras Industrial Applications In-Cabin Entertainment

Consumer Electronics

#### Pin Configuration appears at end of data sheet.

SPI is a trademark of Motorola, Inc.

#### **Features**

- ♦ 256 User-Defined Characters or Pictographs in Integrated EEPROM

- ♦ 12 x 18 Pixel Character Size

- Blinking, Inverse, and Background Control Character Attributes

- ♦ Selectable Brightness by Row

- ♦ Displays Up to 16 Rows x 30 Characters

- ♦ Sag Compensation On Video-Driver Output

- ♦ LOS, VSYNC, HSYNC, and Clock Outputs

- ♦ Internal Sync Generator

- **♦ NTSC and PAL Compatible**

- **♦ SPI-Compatible Serial Interface**

- **♦** Delivered with Preprogrammed Character Set

#### **Ordering Information**

| PART        | PIN-PACKAGE  | LANGUAGE             |

|-------------|--------------|----------------------|

| MAX7456EUI+ | 28 TSSOP-EP* | English/<br>Japanese |

<sup>\*</sup>EP = Exposed pad.

**Note:** This device is specified over the -40°C to +85°C operating temperature range.

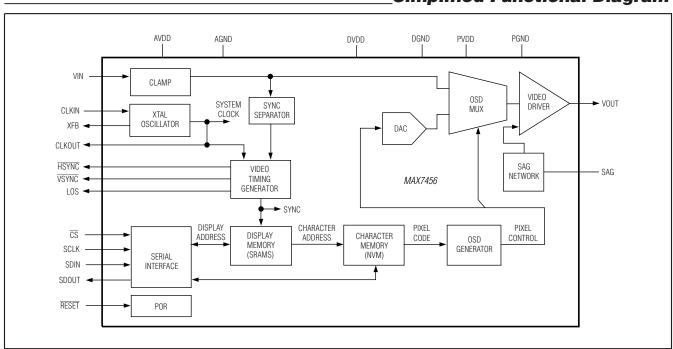

#### Simplified Functional Diagram

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maximintegrated.com.

<sup>+</sup>Denotes a lead-free/RoHS-compliant package.

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

#### **ABSOLUTE MAXIMUM RATINGS**

| AVDD to AGND              | 0.3V to +6V                        |

|---------------------------|------------------------------------|

| DVDD to DGND              | 0.3V to +6V                        |

| PVDD to PGND              | 0.3V to +6V                        |

| AGND to DGND              | 0.3V to +0.3V                      |

| AGND to PGND              | 0.3V to +0.3V                      |

| DGND to PGND              | 0.3V to +0.3V                      |

| VIN, VOUT, SAG to AGND    | 0.3V to (V <sub>AVDD</sub> + 0.3V) |

| HSYNC, VSYNC, LOS to AGND | 0.3V to +6V                        |

| RESET to AGND             | 0.3V to (V <sub>AVDD</sub> + 0.3V) |

| CLKIN, CLKOUT, XFB to DGND0.3<br>SDIN, SCLK, CS, SDOUT to DGND0.3 |                |

|-------------------------------------------------------------------|----------------|

| Maximum Continuous Current into VOLT                              |                |

| Continuous Power Dissipation ( $T_A = +70$ °C)                    |                |

| 28-Pin TSSOP (derate 27mW/°C above +                              | 70°C)2162mW*   |

| Operating Temperature Range                                       | 40°C to +85°C  |

| Junction Temperature                                              | +150°C         |

| Storage Temperature Range                                         | 60°C to +150°C |

| Lead Temperature (soldering, 10s)                                 | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{AVDD} = +4.75 \text{V to } +5.25 \text{V}, V_{DVDD} = +4.75 \text{V to } +5.25 \text{V}, V_{PVDD} = +4.75 \text{V to } +5.25 \text{V}, T_A = T_{MIN} \text{ to } T_{MAX}. \text{ Typical values are at } V_{AVDD} = V_{DVDD} = V_{DVDD} = +5 \text{V}, T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.}) \text{ (Note 1)}$

| PARAMETER                 | SYMBOL                          | CONDITIONS                                                                                            |      | TYP     | MAX  | UNITS  |

|---------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------|------|---------|------|--------|

| POWER SUPPLIES            |                                 |                                                                                                       |      |         |      |        |

| Analog Supply Voltage     | Vavdd                           |                                                                                                       | 4.75 | 5       | 5.25 | V      |

| Digital Supply Voltage    | V <sub>DVDD</sub>               |                                                                                                       | 4.75 | 5       | 5.25 | V      |

| Driver Supply Voltage     | V <sub>P</sub> VDD              |                                                                                                       | 4.75 | 5       | 5.25 | V      |

| Analog Supply Current     | lavdd                           | $V_{IN}$ = 1V <sub>P-P</sub> (100% white flat field signal), VOUT load, R <sub>L</sub> = 150 $\Omega$ |      | 24      | 35   | mA     |

| Digital Supply Current    | I <sub>DVDD</sub>               | $V_{IN}$ = 1V <sub>P-P</sub> (100% white flat field signal), VOUT load, R <sub>L</sub> = 150 $\Omega$ |      | 25      | 30   | mA     |

| Driver Supply Current     | IPVDD                           | $V_{IN}$ = 1V <sub>P-P</sub> (100% white flat field signal), VOUT load, R <sub>L</sub> = 150 $\Omega$ |      | 58      | 80   | mA     |

| NONVOLATILE MEMORY        |                                 |                                                                                                       |      |         |      |        |

| Data Retention            |                                 | $T_A = +25^{\circ}C$                                                                                  |      | 100     |      | Years  |

| Endurance                 |                                 | T <sub>A</sub> = +25°C                                                                                |      | 100,000 |      | Stores |

| DIGITAL INPUTS (CS, SDIN, | RESET, SCLK)                    |                                                                                                       |      |         |      |        |

| Input High Voltage        | VIH                             |                                                                                                       | 2.0  |         |      | V      |

| Input Low Voltage         | VIL                             |                                                                                                       |      |         | 0.8  | V      |

| Input Hysteresis          | VHYS                            |                                                                                                       |      | 50      |      | mV     |

| Input Leakage Current     |                                 | $V_{IN} = 0$ or $V_{DVDD}$                                                                            |      |         | ±10  | μΑ     |

| Input Capacitance         | CIN                             |                                                                                                       |      | 5       |      | рF     |

| DIGITAL OUTPUTS (SDOUT,   | CLKOUT, $\overline{\text{VSY}}$ | NC, HSYNC, LOS)                                                                                       |      |         |      |        |

| Output High Voltage       | V <sub>OH</sub>                 | I <sub>SOURCE</sub> = 4mA (SDOUT, CLKOUT) 2.4                                                         |      |         |      | V      |

| Output Low Voltage        | V <sub>OL</sub>                 | I <sub>SINK</sub> = 4mA                                                                               |      |         | 0.45 | V      |

| Tri-State Leakage Current |                                 | SDOUT, $\overline{CS} = V_{DVDD}$                                                                     |      |         | ±10  | μΑ     |

<sup>\*</sup>As per JEDEC51 Standard (Multilayer Board).

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = +4.75V \text{ to } +5.25V, V_{DVDD} = +4.75V \text{ to } +5.25V, V_{PVDD} = +4.75V \text{ to } +5.25V, T_A = T_{MIN} \text{ to } T_{MAX}.$  Typical values are at  $V_{AVDD} = V_{DVDD} = V_{PVDD} = +5V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                      | SYMBOL                                  | CONDITIONS                                                      | MIN        | TYP  | MAX        | UNITS            |

|--------------------------------|-----------------------------------------|-----------------------------------------------------------------|------------|------|------------|------------------|

| CLOCK INPUT (CLKIN)            |                                         |                                                                 | •          |      |            |                  |

| Clock Frequency                |                                         |                                                                 |            | 27   |            | MHz              |

| Clock-Pulse High               |                                         |                                                                 | 14         |      |            | ns               |

| Clock-Pulse Low                |                                         |                                                                 | 14         |      |            | ns               |

| Lavard I Bada Malka ara        |                                         |                                                                 | 0.7 x      |      |            | 1/               |

| Input High Voltage             |                                         |                                                                 | $V_{DVDD}$ |      |            | V                |

|                                |                                         |                                                                 |            |      | 0.3 x      |                  |

| Input Low Voltage              |                                         |                                                                 |            |      | $V_{DVDD}$ | V                |

| Input Leakage Current          |                                         | V <sub>IN</sub> = 0V or V <sub>DVDD</sub>                       |            |      | ±50        | μΑ               |

| CLOCK OUTPUT (CLKOUT)          |                                         |                                                                 | 1          |      |            |                  |

| Duty Cycle                     |                                         | 5pF and 10kΩ to DGND                                            | 40         | 50   | 60         | %                |

| Rise Time                      |                                         | 5pF and 10kΩ to DGND                                            |            | 3    |            | ns               |

| Fall Time                      |                                         | 5pF and 10kΩ to DGND                                            |            | 3    |            | ns               |

| VIDEO CHARACTERISTICS          | •                                       |                                                                 | 1          |      |            |                  |

| DC Davier Cumply Dainstinn     |                                         | V <sub>AVDD</sub> = V <sub>DVDD</sub> = V <sub>PVDD</sub> = 5V; |            | 40   |            | ٩D               |

| DC Power-Supply Rejection      |                                         | V <sub>IN</sub> = 1V <sub>P-P</sub> , measured at VOUT          |            | 40   |            | dB               |

|                                |                                         | VAVDD = VDVDD = VPVDD = 5V;                                     |            |      |            |                  |

| AC Power-Supply Rejection      |                                         | V <sub>IN</sub> = 1V <sub>P-P</sub> , measured at VOUT;         |            | 30   |            | dB               |

|                                |                                         | f = 5MHz; power-supply ripple = 0.2V <sub>P-P</sub>             |            |      |            |                  |

| Short-Circuit Current          |                                         | VOUT to PGND                                                    |            |      | 230        | mA               |

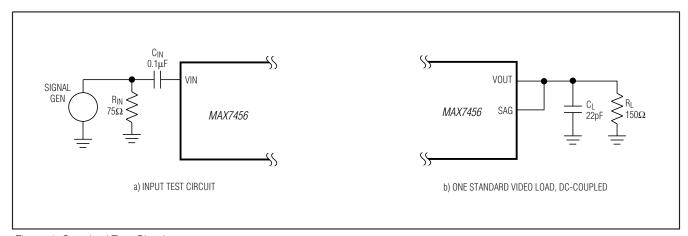

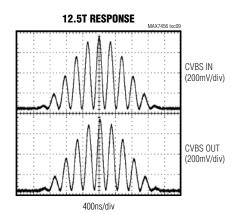

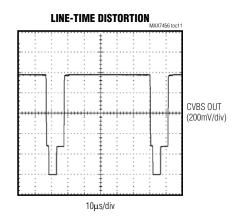

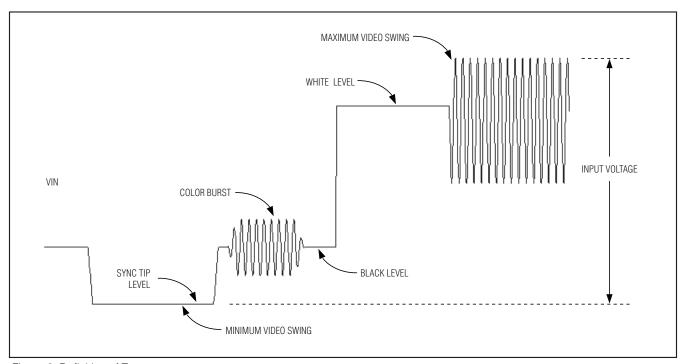

| Line-Time Distortion           | LTD                                     | Figures 1a, 1b                                                  |            |      | 0.5        | %                |

| Output Impedance               | Z <sub>OUT</sub>                        | Figures 1a, 1b                                                  |            | 0.2  |            | Ω                |

| Gain                           |                                         | Figures 1a, 1b                                                  | 1.89       | 2.0  | 2.11       | V/V              |

| Black Level                    |                                         | At VOLIT Figures 15, 16                                         |            |      | AGND       | V                |

| DIACK Level                    |                                         | At VOUT, Figures 1a, 1b                                         |            |      | + 1.5      | V                |

| Input-Voltage Operating Range  | V <sub>IN</sub>                         | Figures 1a, 3 (Note 2)                                          | 0.5        |      | 1.2        | V <sub>P-P</sub> |

| Input-Voltage Sync Detection   | \/\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | Figures 1s, 2 (Nets 2)                                          | 0.5        |      | 2.0        | \/p =            |

| Range                          | VINSD                                   | Figures 1a, 3 (Note 3)                                          | 0.5        |      | 2.0        | V <sub>P-P</sub> |

| Maximum Output-Voltage Swing   | Vout                                    | Figures 1a, 1b                                                  | 2.4        |      |            | V <sub>P-P</sub> |

| Output-Voltage Sync Tip Level  |                                         |                                                                 |            | 0.7  |            | V                |

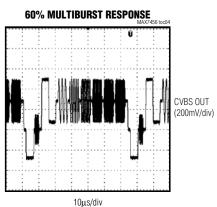

| Large Signal Bandwidth (0.2dB) | BW                                      | V <sub>OUT</sub> = 2V <sub>P-P</sub> , Figures 1a, 1b           |            | 6    |            | MHz              |

| VIN to VOUT Delay              |                                         |                                                                 |            | 30   |            | ns               |

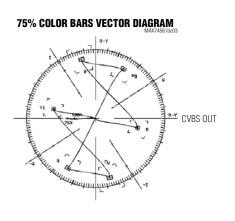

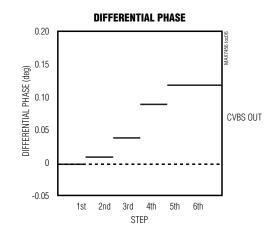

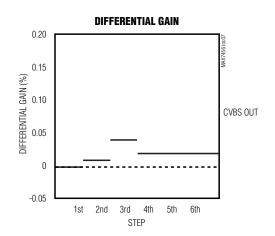

| Differential Gain              | DG                                      |                                                                 |            | 0.5  |            | %                |

| Differential Phase             | DP                                      |                                                                 |            | 0.5  |            | Degrees          |

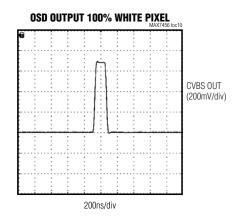

| OSD White Level                |                                         | VOUT 100% white level with respect to black level               | 1.25       | 1.33 | 1.45       | V                |

| Horizontal Pixel Jitter        |                                         | Between consecutive horizontal lines                            |            | 24   |            | ns               |

| Video Clamp Settling Time      |                                         |                                                                 |            | 32   |            | Lines            |

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = +4.75V \text{ to } +5.25V, V_{DVDD} = +4.75V \text{ to } +5.25V, V_{PVDD} = +4.75V \text{ to } +5.25V, T_A = T_{MIN} \text{ to } T_{MAX}$ . Typical values are at  $V_{AVDD} = V_{DVDD} = V_{PVDD} = +5V, T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                     | SYMBOL              | SYMBOL CONDITIONS                                |  | TYP | MAX | UNITS |  |

|-------------------------------|---------------------|--------------------------------------------------|--|-----|-----|-------|--|

| OSD CHARACTERISTICS           | OSD CHARACTERISTICS |                                                  |  |     |     |       |  |

| OSD Rise Time                 |                     | OSD insertion mux register<br>OSDM[5,4,3] = 011b |  | 60  |     | ns    |  |

| OSD Fall Time                 |                     | OSD insertion mux register<br>OSDM[5,4,3] = 011b |  | 60  |     | ns    |  |

| OSD Insertion Mux Switch Time |                     | OSD insertion mux register<br>OSDM[2,1,0] = 011b |  | 75  |     | ns    |  |

#### TIMING CHARACTERISTICS

$(V_{AVDD} = +4.75V \text{ to } +5.25V, V_{DVDD} = +4.75V \text{ to } +5.25V, V_{PVDD} = +4.75V \text{ to } +5.25V, T_A = T_{MIN} \text{ to } T_{MAX}.$  Typical values are at  $V_{AVDD} = V_{DVDD} = V_{PVDD} = +5V, T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                             | SYMBOL                                                 | CONDITIONS                       | MIN | TYP | MAX | UNITS |

|-------------------------------------------------------|--------------------------------------------------------|----------------------------------|-----|-----|-----|-------|

| SPI TIMING                                            |                                                        |                                  | •   |     |     | •     |

| SCLK Period                                           | tCP                                                    |                                  | 100 |     |     | ns    |

| SCLK Pulse-Width High                                 | tсн                                                    |                                  | 40  |     |     | ns    |

| SCLK Pulse-Width Low                                  | tCL                                                    |                                  | 40  |     |     | ns    |

| CS Fall to SCLK Rise Setup                            | tcsso                                                  |                                  | 30  |     |     | ns    |

| CS Fall After SCLK Rise Hold                          | tCSH0                                                  |                                  | 0   |     |     | ns    |

| CS Rise to SCLK Setup                                 | tCSS1                                                  |                                  | 30  |     |     | ns    |

| CS Rise After SCLK Hold                               | tCSH1                                                  |                                  | 0   |     |     | ns    |

| CS Pulse-Width High                                   | tcsw                                                   |                                  | 100 |     |     | ns    |

| SDIN to SCLK Setup                                    | t <sub>DS</sub>                                        |                                  | 30  |     |     | ns    |

| SDIN to SCLK Hold                                     | tDH                                                    |                                  | 0   |     |     | ns    |

| SDOUT Valid Before SCLK                               | t <sub>DO1</sub>                                       | 20pF to ground                   | 25  |     |     | ns    |

| SDOUT Valid After SCLK                                | t <sub>DO2</sub>                                       | 20pF to ground                   | 0   |     |     | ns    |

| CS High to SDOUT High Impedance                       | t <sub>DO3</sub>                                       | 20pF to ground                   | 300 |     |     | ns    |

| CS Low to SDOUT Logic Level                           | t <sub>DO4</sub>                                       | 20pF to ground                   | 20  |     |     | ns    |

| HSYNC, VSYNC, AND LOS TIMI                            | NG                                                     |                                  |     |     |     |       |

| LOS, VSYNC, and HSYNC Valid before CLKOUT Rising Edge | t <sub>DOV</sub>                                       | 20pF to ground 30                |     | 30  |     | ns    |

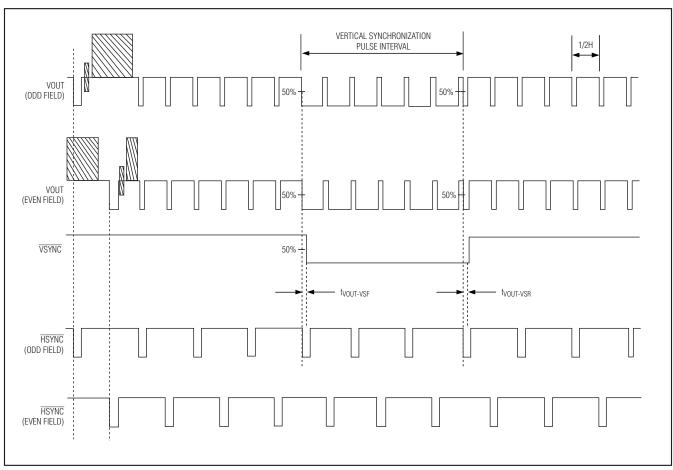

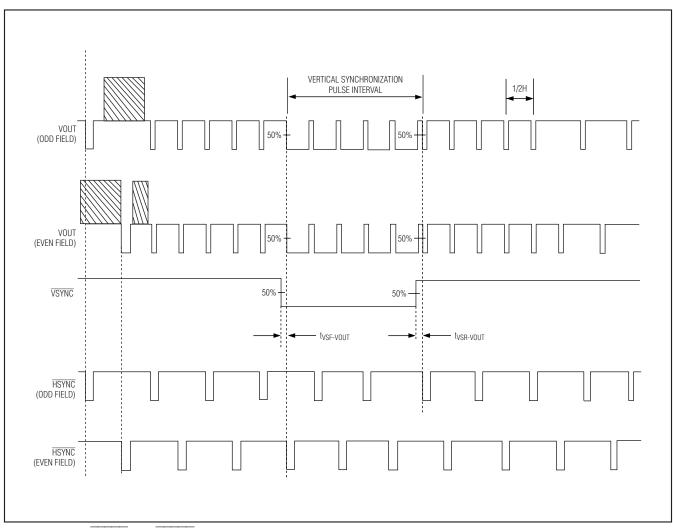

| VOUT Sync to VSYNC Falling                            | to VSYNC Falling NTSC external sync mode, Figure 4 375 |                                  |     |     |     |       |

| Edge Delay                                            | tvout-vsf                                              | PAL external sync mode, Figure 6 |     | 400 |     | ns    |

#### **TIMING CHARACTERISTICS (continued)**

$(V_{AVDD} = +4.75V \text{ to } +5.25V, V_{DVDD} = +4.75V \text{ to } +5.25V, V_{PVDD} = +4.75V \text{ to } +5.25V, T_A = T_{MIN} \text{ to } T_{MAX}.$  Typical values are at  $V_{AVDD} = V_{DVDD} = V_{PVDD} = +5V, T_A = +25^{\circ}C,$  unless otherwise noted.) (Note 1)

| PARAMETER                             | SYMBOL           | CONDITIONS                                | MIN | TYP | MAX | UNITS |

|---------------------------------------|------------------|-------------------------------------------|-----|-----|-----|-------|

| VOUT Sync to VSYNC Rising             | tuout von        | NTSC external sync mode, Figure 4         |     | 400 |     | no    |

| Edge Delay                            | tvout-vsr        | PAL external sync mode, Figure 6          |     | 425 |     | ns    |

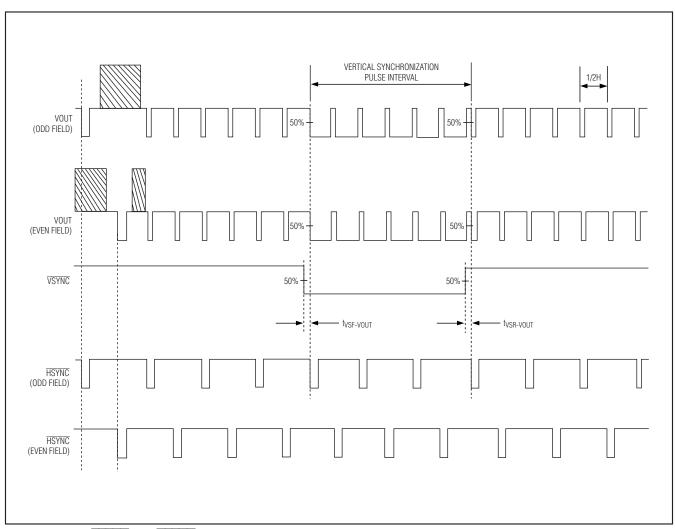

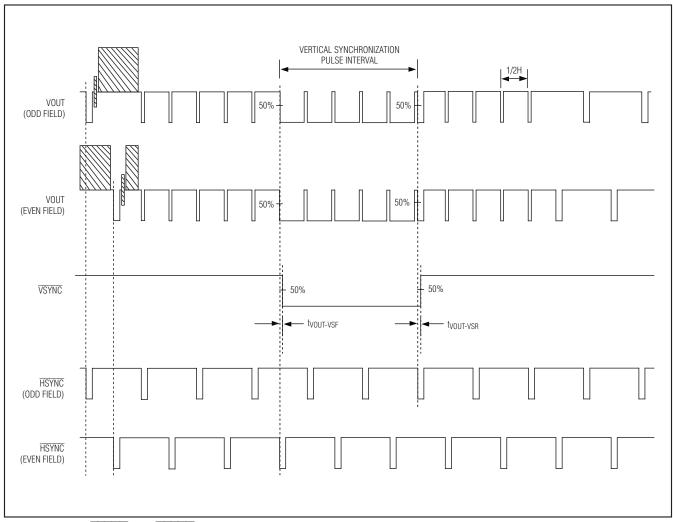

| VSYNC Falling Edge to VOUT            | t. (05.) (01.) T | NTSC internal sync mode, Figure 5         |     | 40  |     | no    |

| Sync Delay                            | tvsf-vout        | PAL internal sync mode, Figure 7          |     | 45  |     | ns    |

| VSYNC Rising Edge to VOUT             | tuon volut       | NTSC internal sync mode, Figure 5         |     | 32  |     | ns    |

| Sync Delay                            | tvsr-vout        | PAL internal sync mode, Figure 7          | 30  |     |     | 115   |

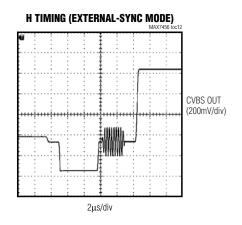

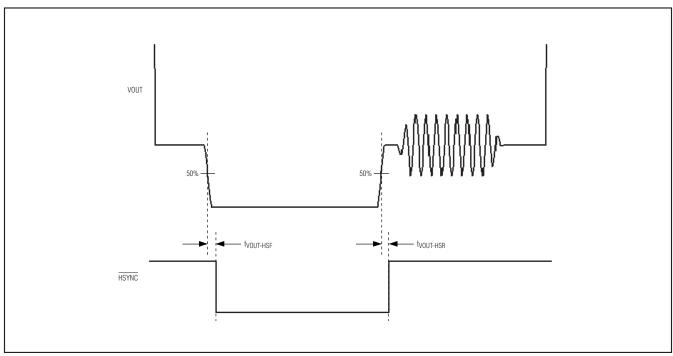

| VOUT Sync to HSYNC Falling Edge Delay | tvour-HSF        | NTSC and PAL external sync mode, Figure 8 | 310 |     |     | ns    |

| VOUT Sync to HSYNC Rising Edge Delay  | tvout-HSR        | NTSC and PAL external sync mode, Figure 8 |     | 325 |     | ns    |

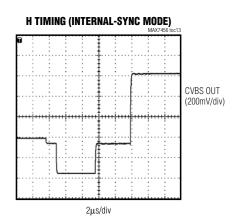

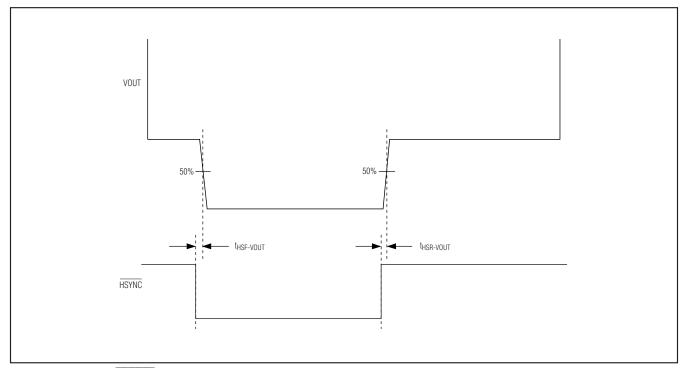

| HSYNC Falling Edge to VOUT Sync Delay | tHSF-VOUT        | NTSC and PAL internal sync mode, Figure 9 |     | 115 |     | ns    |

| HSYNC Rising Edge to VOUT Sync Delay  | thsr-vout        | NTSC and PAL internal sync mode, Figure 9 |     | 115 |     | ns    |

| All Supplies High to CS Low           | tpup             | Power-up delay                            |     | 50  |     | ms    |

| NVM Write Busy                        | t <sub>NVW</sub> |                                           |     | 12  |     | ms    |

Note 1: See the standard test circuits of Figure 1.  $R_L = 75\Omega$ , unless otherwise specified. All digital input signals are timed from a voltage level of  $(V_{IH} + V_{IL}) / 2$ . All parameters are tested at  $T_A = +85$ °C and values through temperature range are guaranteed by design.

Note 2: The input-voltage operating range is the input range over which the output signal parameters are guaranteed (Figure 3).

**Note 3:** The input-voltage sync detection range is the input composite video range over which an input sync signal is properly detected and the OSD signal appears at VOUT. However, the output voltage specifications are not guaranteed for input signals exceeding the maximum specified in the input operating voltage range (Figure 3).

Figure 1. Standard Test Circuits

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

#### **Typical Operating Characteristics**

(VAVDD = +5V, VDVDD = +5V, VPVDD = +5V, TA = +25°C, unless otherwise noted. See the *Typical Operating Circuit* of Figure 2, if applicable.)

#### **IMAGE WITH ON-SCREEN GRAPHICS**

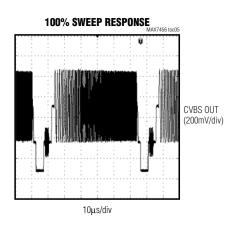

# 100% COLOR BARS RESPONSE MAX7456 toc02 CVBS OUT (200mV/div

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

#### Typical Operating Characteristics (continued)

(VAVDD = +5V, VDVDD = +5V, VPVDD = +5V, TA = +25°C, unless otherwise noted. See the *Typical Operating Circuit* of Figure 2, if applicable.)

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

#### \_Typical Operating Characteristics (continued)

(V<sub>AVDD</sub> = +5V, V<sub>DVDD</sub> = +5V, V<sub>PVDD</sub> = +5V, T<sub>A</sub> = +25°C, unless otherwise noted. See the *Typical Operating Circuit* of Figure 2, if applicable.)

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

#### **Pin Description**

| PIN                    | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                           |

|------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 13–16,<br>27, 28 | N.C.   | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                           |

| 3                      | DVDD   | Digital Power-Supply Input. Bypass to DGND with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                 |

| 4                      | DGND   | Digital Ground                                                                                                                                                                                                                                                                                                                                                     |

| 5                      | CLKIN  | Crystal Connection 1. Connect a parallel resonant, fundamental mode crystal between CLKIN and XFB for use as a crystal oscillator, or drive CLKIN directly with a 27MHz system reference clock.                                                                                                                                                                    |

| 6                      | XFB    | Crystal Connection 2. Connect a parallel resonant, fundamental mode crystal between CLKIN and XFB for use as a crystal oscillator, or leave XFB unconnected when driving CLKIN with a 27MHz system reference clock.                                                                                                                                                |

| 7                      | CLKOUT | Clock Output. 27MHz logic-level output system clock.                                                                                                                                                                                                                                                                                                               |

| 8                      | CS     | Active-Low Chip-Select Input. SDOUT goes high impedance when $\overline{\text{CS}}$ is high.                                                                                                                                                                                                                                                                       |

| 9                      | SDIN   | Serial Data Input. Data is clocked in at rising edge of SCLK.                                                                                                                                                                                                                                                                                                      |

| 10                     | SCLK   | Serial Clock Input. Clocks data into SDIN and out of SDOUT. Duty cycle must be between 40% and 60%.                                                                                                                                                                                                                                                                |

| 11                     | SDOUT  | Serial Data Output. Data is clocked out at the falling edge of SCLK. High impedance when $\overline{\text{CS}}$ is high.                                                                                                                                                                                                                                           |

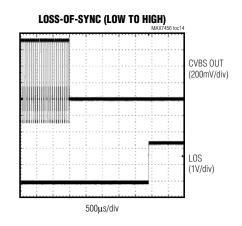

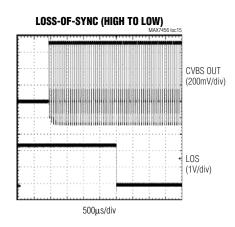

| 12                     | LOS    | Loss-of-Sync Output (Open-Drain). LOS goes high when the VIN sync pulse is lost for 32 consecutive lines. LOS goes low when 32 consecutive valid sync pulses are received. Connect to a $1k\Omega$ pullup resistor to DVDD or another positive supply voltage suitable for the receiving device.                                                                   |

| 17                     | VSYNC  | Vertical Sync Output (Open-Drain). $\overline{\text{VSYNC}}$ goes low following the video input's vertical sync interval. $\overline{\text{VSYNC}}$ is either recovered from VIN or internally generated when in internal sync mode. Connect to a 1k $\Omega$ pullup resistor to DVDD or another positive supply voltage suitable for the receiving device.        |

| 18                     | HSYNC  | Horizontal Sync Output (Open-Drain). $\overline{\text{HSYNC}}$ goes low following the video input's horizontal sync interval. $\overline{\text{HSYNC}}$ is either recovered from VIN or internally generated when in internal sync mode. Connect to a 1k $\Omega$ pullup resistor to DVDD or another positive supply voltage suitable for the receiving device.    |

| 19                     | RESET  | System Reset Input. The minimum RESET pulse width is 50ms. All SPI registers are reset to their default values after 100µs following the rising edge of RESET. These registers are not accessible for reading or writing during that time. The display memory is reset to its default value of 00H in all locations after 20µs following the rising edge of RESET. |

| 20                     | AGND   | Analog Ground                                                                                                                                                                                                                                                                                                                                                      |

| 21                     | AVDD   | Analog Power-Supply Input. Bypass to AGND with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                  |

| 22                     | VIN    | PAL or NTSC CVBS Video Input                                                                                                                                                                                                                                                                                                                                       |

| 23                     | PGND   | Driver Ground. Connect to AGND at a single point.                                                                                                                                                                                                                                                                                                                  |

| 24                     | PVDD   | Driver Power-Supply Input. Bypass to PGND with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                  |

| 25                     | SAG    | Sag Correction Input. Connect to VOUT if not used. See Figure 1b.                                                                                                                                                                                                                                                                                                  |

| 26                     | VOUT   | Video Output                                                                                                                                                                                                                                                                                                                                                       |

| _                      | EP     | Exposed Pad. Internally connected to AGND. Connect EP to the AGND plane for improved heat dissipation. Do not use EP as the only ground connection.                                                                                                                                                                                                                |

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

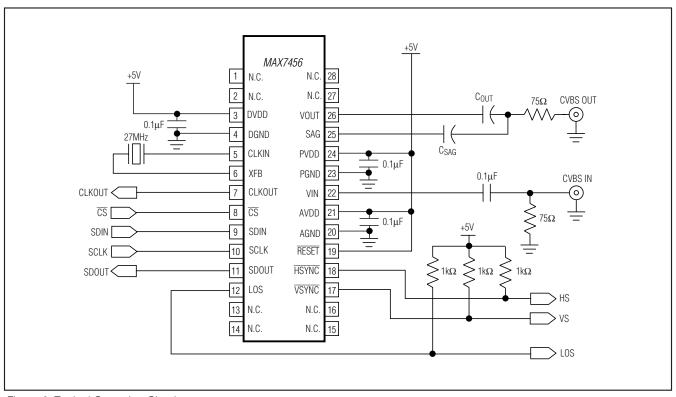

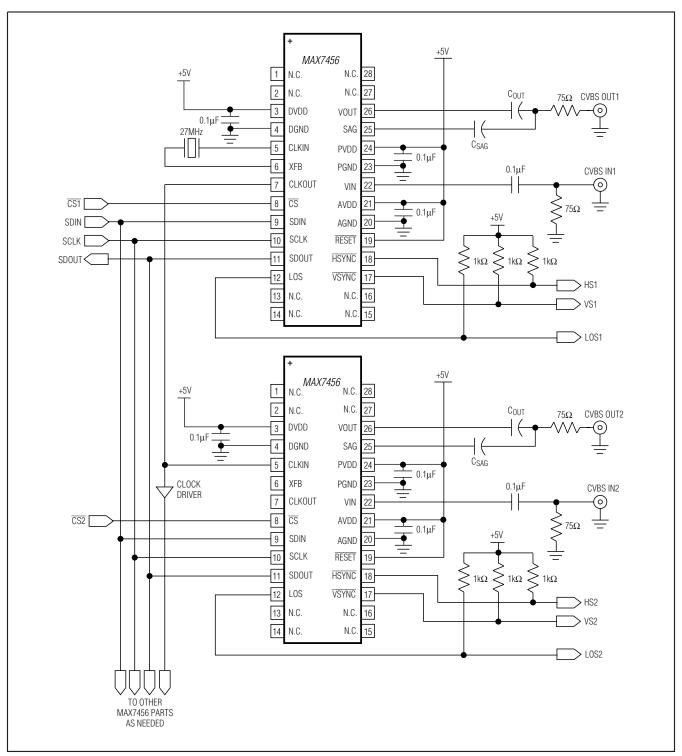

Figure 2. Typical Operating Circuit

#### **Detailed Description**

The MAX7456 single-channel monochrome on-screen display (OSD) generator integrates all the functions needed to generate a user-defined OSD and insert it into the output signal. The MAX7456 accepts a composite NTSC or PAL video signal. The device includes an input clamp, sync separator, video timing generator, OSD insertion mux, nonvolatile character memory, display memory, OSD generator, crystal oscillator, an SPI-compatible interface to read/write the OSD data, and a video driver (see the *Simplified Functional Diagram*). Additionally, the MAX7456 provides vertical sync (VSYNC), horizontal sync (HSYNC), and loss-of sync (LOS) outputs for system synchronization. A clock output signal (CLKOUT) allows daisy-chaining of multiple devices.

See the *MAX7456 Register Description* section for an explanation of register notation use in this data sheet.

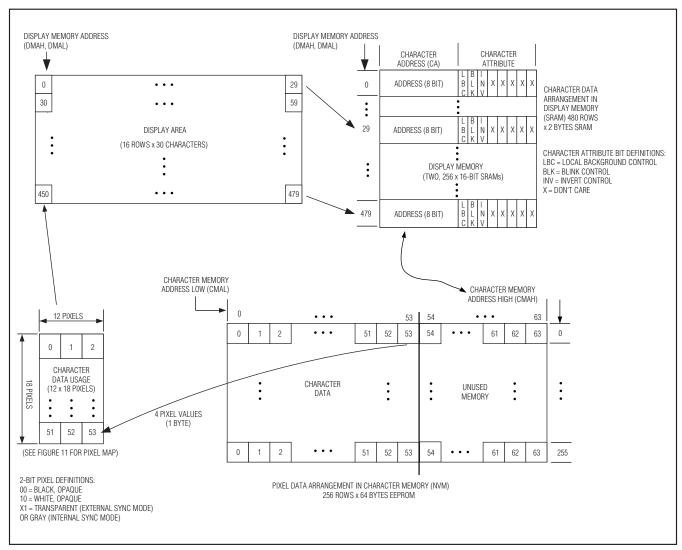

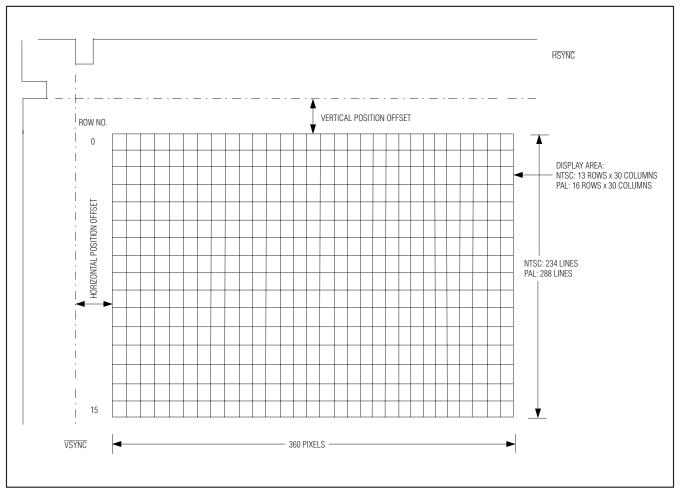

The 256 user-defined 12 x 18 pixel character set comes preloaded and is combined with the input video stream to generate a CVBS signal with OSD video output. A maximum of 256 12 x 18 pixel characters can be reprogrammed in the NVM. In NTSC mode, 13 rows x 30 characters are displayed. In PAL mode, 16 rows x 30 characters are displayed. When the input video signal is absent, the OSD image can still be displayed by using the MAX7456's internal video timing generator.

#### **Video Input**

The MAX7456 accepts standard NTSC or PAL CVBS signals at VIN. The video signal input must be AC-coupled with a  $0.1\mu F$  capacitor and is internally clamped. An input coupling capacitance of  $0.1\mu F$  is required to guarantee the specified line-time distortion (LTD) and video clamp settling time. The video clamp settling time changes proportionally to the input coupling capacitance, and LTD changes inversely proportional to the capacitance.

### Single-Channel Monochrome On-Screen Display with Integrated EEPROM

Figure 3. Definition of Terms

#### **Input Clamp**

The MAX7456's clamp is a DC-restore circuit that uses the input coupling capacitor to correct any DC shift of the input signal, on a line-by-line basis, such that the sync tip at VIN is approximately 550mV. This establishes a DC level at VIN suitable for the on-chip sync detection and video processing functions. This circuitry also removes low-frequency noise such as 60Hz hum or other additive low-frequency noise.

#### Sync Separator

The sync separator detects the composite sync pulses on the video input and extracts the timing information to generate HSYNC and VSYNC. It is also used for internal OSD synchronization and loss-of-sync (LOS) detection. LOS goes high if no sync signal is detected at VIN for 32 consecutive lines, and goes low if 32 consecutive horizontal sync signals are detected. During a LOS condition, when VM0[5] = 0 (Video Mode 0 register, bit 5), only the OSD appears at the VOUT. At this time, the input image is set to a gray level at VOUT as determined by VM1[6:4]. The behavior of all sync modes is shown in Table 1.

**Table 1. Video Sync Modes**

| VIDEO MODE            | VIN      | VSYNC           | HSYNC           | LOS  | VOUT                  |

|-----------------------|----------|-----------------|-----------------|------|-----------------------|

| Auto Sync Select Mode | Video    | Active          | Active          | Low  | V <sub>IN</sub> + OSD |

| VM0[5, 4] = 0x        | No input | Active          | Active          | High | OSD only              |

| External Sync Select  | Video    | Active          | Active          | Low  | V <sub>IN</sub> + OSD |

| VM0[5, 4] = 10        | No input | Inactive (high) | Inactive (high) | High | DC                    |

| Internal Sync Select  | Video    | Active          | Active          | High | OSD only              |

| VM0[5, 4] = 11        | No input | Active          | Active          | High | OSD only              |

X = Don't care.

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

#### **Video Timing Generator**

The video timing generator is a digital circuit generating all internal and external (VSYNC and HSYNC) timing signals. VSYNC and HSYNC can be synchronized to VIN, or run independently of any input when in internal sync mode. The video timing generator can generate NTSC or PAL timing using the same 27MHz crystal (see Figures 4–9).

#### **Crystal Oscillator**

The internal crystal oscillator generates the system clock used by the video timing generator. The oscillator uses a 27MHz crystal or can be driven by an external 27MHz TTL clock at CLKIN. For external clock mode, connect the 27MHz TTL input clock to CLKIN and leave XFB unconnected.

#### **Display Memory (SRAM)**

The display memory stores 480 character addresses that point to the characters stored in the NVM character memory. The content of the display memory is user-programmable through the SPI-compatible serial interface. The display-memory address corresponds to a fixed location on a monitor (see Figure 10). Momentary breakup of the OSD image can be prevented by writing to the display memory during the vertical blanking interval. This can be achieved by using \$\overline{VSYNC}\$ as an interrupt to the host processor to initiate writing to the display memory.

Figure 4. VOUT, VSYNC, and HSYNC Timing (NTSC, External Sync Mode)

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

Figure 5. VOUT, VSYNC, and HSYNC Timing (NTSC, Internal Sync Mode)

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

Figure 6. VOUT, VSYNC, and HSYNC Timing (PAL, External Sync Mode)

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

Figure 7. VOUT, VSYNC, and HSYNC Timing (PAL, Internal Sync Mode)

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

Figure 8. VOUT, and HSYNC Horizontal Sync Timing (NTSC and PAL, External Sync Mode)

Figure 9. VOUT and HSYNC Horizontal Sync Timing (NTSC and PAL, Internal Sync Mode)

#### **Character Memory (NVM)**

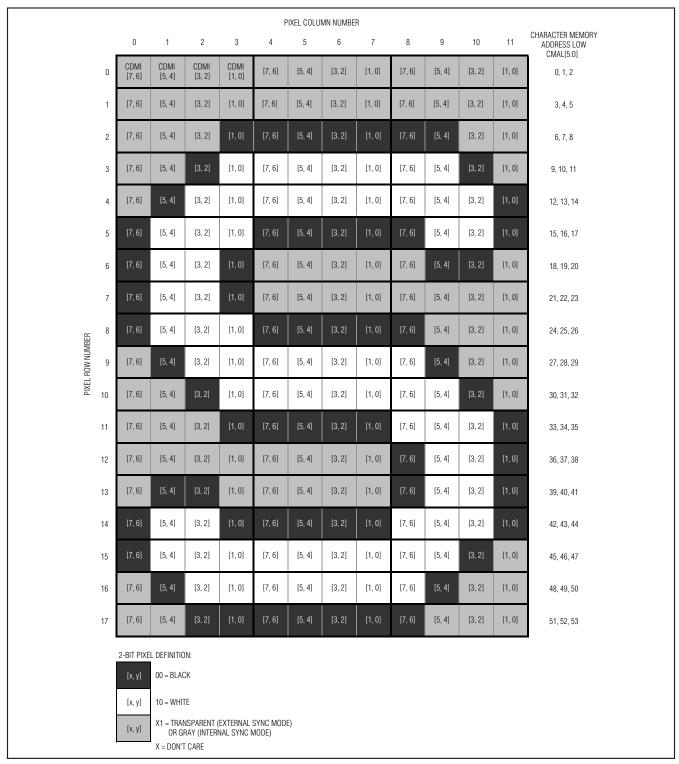

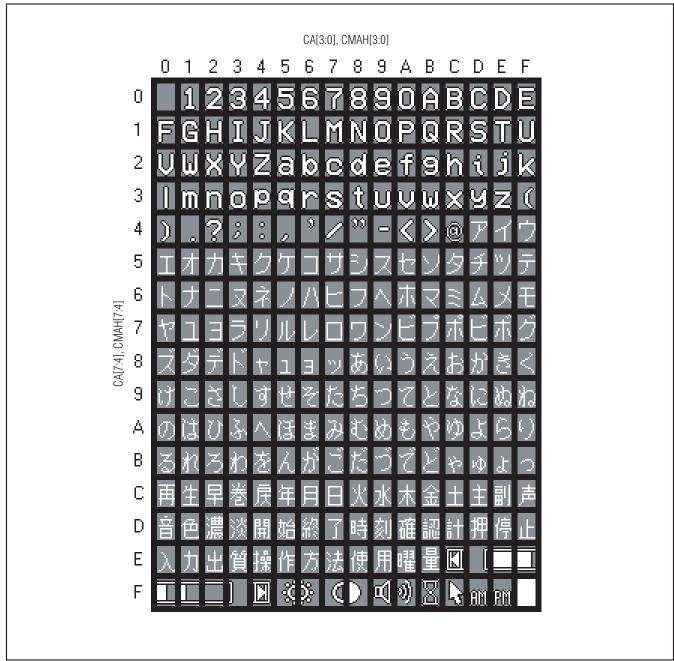

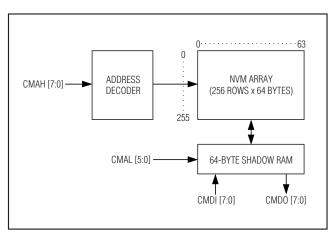

The character memory is a 256-row x 64-byte wide nonvolatile memory (NVM) that stores the characters or graphic images, and is factory preloaded with the characters shown in Figure 12. The content of the character memory is user-programmable through the SPI-compatible serial interface. Each row contains the description of a single OSD character. Each character consists of 12 horizontal x 18 vertical pixels where each pixel is represented by 2 bits of data having three states: white, black, or transparent. Thus, each character requires 54 bytes of pixel data (Figure 11).

The NVM requires reading and writing a whole character (64 bytes) at a time. This is enabled by an additional

row of memory called the shadow RAM. The 64-byte temporary shadow RAM contains all the pixel data of a selected character (CMAH[7:0]) and is used as a buffer for read and write operations to the NVM (Figure 13). Accessing the NVM is always through the shadow RAM, and is thus a two-step process. To write a character to the NVM, the user first fills the shadow RAM using 54 8-bit SPI write operations, and then executes a single shadow RAM write command. Similarly, reading a character's pixel values requires first reading a character's pixel data into the shadow RAM, and then reading the desired pixel data from the shadow RAM to the SPI port.

Figure 10. Definitions of Various Parameters

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

Figure 11. Character Data Usage (Pixel Map)

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

Figure 12. Character Address Map (Default Character Set)

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

Figure 13. NVM Structure

#### On-Screen Display (OSD) Generator

The OSD generator sets each pixel amplitude based on the content of the character memory and Row Brightness registers (RB0-RB15).

#### **OSD** Insertion Mux

The OSD insertion mux selects between an OSD pixel and the input video signal. The OSD image sharpness is controlled by the OSD Rise and Fall Time bits, and the OSD Insertion Mux Switching Time bits, found in the OSD Insertion Mux (OSDM) register. This register controls the trade-off between OSD image sharpness and crosscolor/crossluma artifacts. Lower time settings produce sharper pixels, but potentially greater crosscolor/crossluma artifacts. The optimum setting depends on the requirements of the application and, therefore, can be set by the user.

#### **Video-Driver Output**

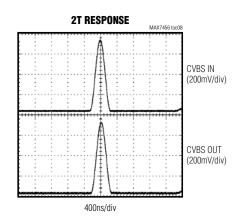

The MAX7456 includes a video-driver output with a gain of 2. The driver has a maximum of  $2.4V_{P-P}$  output swing and a 6MHz large signal bandwidth ( $\leq 0.2dB$  attenuation). The driver output is capable of driving two  $150\Omega$  standard video loads.

#### Sag Correction

Sag correction is a means of reducing the electrical and physical size of the output coupling capacitor while achieving acceptable line-time distortion. Sag correction refers to the low frequency compensation of the highpass filter formed by the  $150\Omega$  load of a back-terminated coaxial cable and the output coupling capacitor. This breakpoint must be low enough in frequency to pass the vertical sync interval (< 25Hz for PAL and < 30Hz for NTSC) to avoid field tilt. Traditionally, the breakpoint is made < 5Hz, and the coupling capacitor

must be very large, typically >  $330\mu F$ . The MAX7456 reduces the value of this capacitor, replacing it with two smaller capacitors (C<sub>OUT</sub> and C<sub>SAG</sub>), substantially reducing the size and cost of the coupling capacitors while achieving acceptable line-time distortion (Table 2). Connect SAG to VOUT if not used.

**Table 2. SAG-Correction Capacitor Values**

| C <sub>OUT</sub> (μF) | C <sub>SAG</sub> (µF) | LINE-TIME DISTORTION (% typ) |

|-----------------------|-----------------------|------------------------------|

| 470                   | _                     | 0.2                          |

| 100                   | _                     | 0.4                          |

| 100                   | 22                    | 0.3                          |

| 47                    | 47                    | 0.3                          |

| 22                    | 22                    | 0.4                          |

| 10                    | 10                    | 0.6                          |

#### Serial Interface

The SPI-compatible serial interface programs the operating modes and OSD data. Read capability permits write verification and reading the Status (STAT), Display Memory Data Out (DMDO), and Character Memory Data Out (CMDO) registers.

#### Read and Write Operations

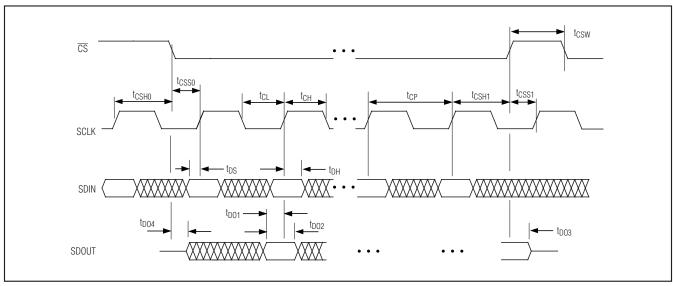

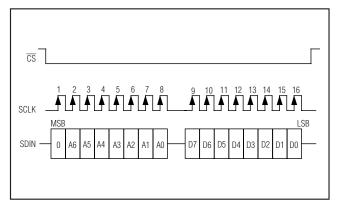

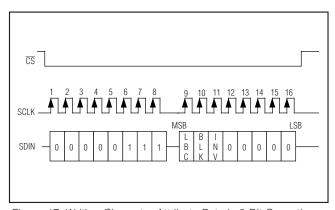

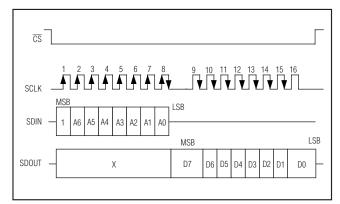

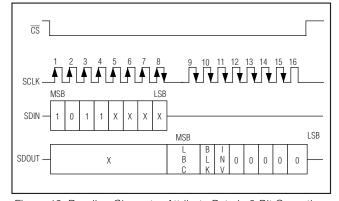

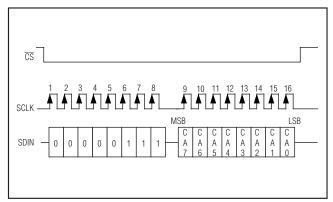

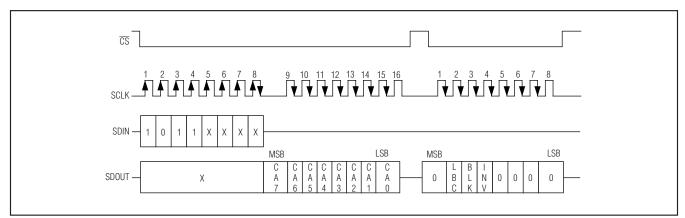

The MAX7456 supports interface clocks (SCLK) up to 10MHz. Figure 15 illustrates writing data and Figure 16 illustrates reading data from the MAX7456. Bring  $\overline{CS}$  low to enable the serial interface. Data is clocked in at SDIN on the rising edge of SCLK. When  $\overline{CS}$  transitions high, data is latched into the input register. If  $\overline{CS}$  goes high in the middle of a transmission, the sequence is aborted (i.e., data does not get written into the registers). After  $\overline{CS}$  is brought low, the device waits for the first byte to be clocked into SDIN to identify the type of data transfer being executed.

The SPI commands are 16 bits long with the 8 most significant bits (MSBs) representing the register address and the 8 least significant bits (LSBs) representing the data (Figures 15 and 16). There are two exceptions to this arrangement:

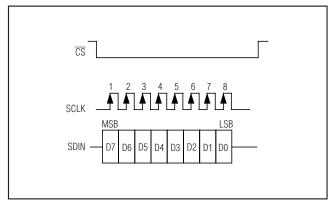

- Auto-increment write mode used for display memory access is a single 8-bit operation (Figure 21). When performing the auto-increment write for the display memory, the 8-bit address is internally generated, and only 8-bit data is required at the serial interface.

- 2) Reading character data from the display memory, when in 16-bit operation mode, is a 24-bit operation (8-bit address plus 16-bit data). See Figure 20.

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

Figure 14. Detailed Serial-Interface Timing

Figure 15. Write Operation

Figure 17. Writing Character Attribute Byte in 8-Bit Operation Mode

Figure 16. Read Operation

Figure 18. Reading Character Attribute Byte in 8-Bit Operation Mode

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

Figure 19. Writing Character Address Byte in 8-Bit and 16-Bit Operation Modes

Figure 20. Reading Character Address and Character Attribute Bytes in 16-Bit Operation Mode

Figure 21. Write Operation in Auto-Increment Mode

#### Resets

#### Power-On Reset

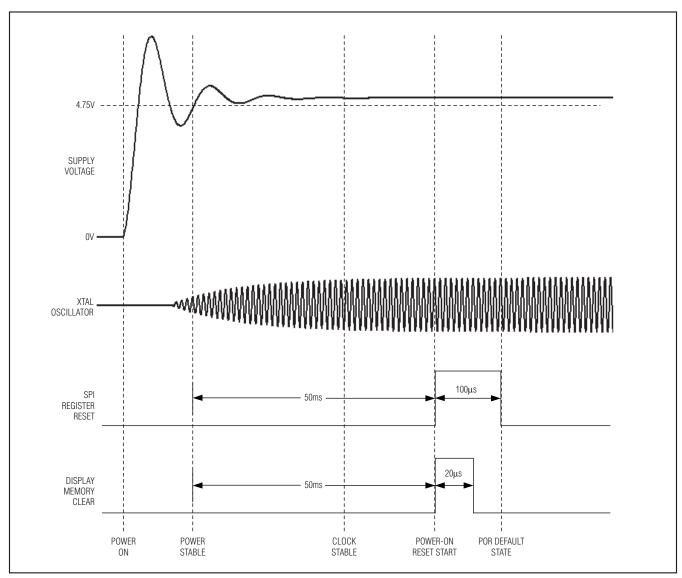

The MAX7456's power-on reset circuitry (POR) provides an internal reset signal that is active after the supply voltage has stabilized. The internal reset signal resets all registers to their default values and clears the display memory. The register reset process requires 100µs, and to avoid unexpected results, read/write activity is not allowed during this interval. The display memory is reset, and the OSD is enabled typically 50ms after the supply voltage has stabilized and a stable 27MHz clock is available. The user should avoid SPI operations during this time to avoid unexpected results. After 50ms (typical), STAT[6] can be polled to verify that the reset sequence is complete (Figure 22).

Figure 22. Power-On Reset Sequence

#### Software Reset

The MAX7456 features a Software Reset bit (VM0[1]) that, when set high, clears the display memory and resets all registers to their default values except the OSD Black Level register (OSDBL). After 100µs (typical), STAT[6] can be polled to verify that the reset process is complete.

#### Hardware Reset

The MAX7456 provides a hardware reset input (RESET) that functions the same as the POR. All registers are

reset to their default values and are not accessible for reading/writing when  $\overline{\text{RESET}}$  is driven low. The resetting process requires a  $\geq 50\text{ms}$  wide  $\overline{\text{RESET}}$  pulse, and no other activities are allowed during this interval. All SPI registers are reset to their default values 100µs after the rising edge of  $\overline{\text{RESET}}$ . The display memory is reset to its default value of 00H in all locations 20µs after the rising edge of  $\overline{\text{RESET}}$ .  $\overline{\text{RESET}}$  takes precedence over the Software Reset bit. After  $\overline{\text{RESET}}$  has been deasserted, STAT[6] can be polled to verify that the reset sequence is complete.

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

#### \_MAX7456 Register Description

Access to all MAX7456 operations, including displaymemory and character-memory access, are through the SPI registers listed in Table 3. There is no direct access to the display and character memories through the SPI port. See the *Applications Information* section

for step-by-step descriptions of the SPI operations needed to access the memories.

The register format used in this data sheet is REGISTER\_NAME [BIT\_NUMBERS]. For example, bit 1 in Video Mode 0 register is written as VM0[1].

**Table 3. Register Map**

| WRITE<br>ADDRESS | READ<br>ADDRESS | REGISTER<br>NAME | REGISTER<br>DESCRIPTION       |

|------------------|-----------------|------------------|-------------------------------|

| 00H              | 80H             | VMO              | Video Mode 0                  |

| 01H              | 81H             | VM1              | Video Mode 1                  |

| 02H              | 82H             | HOS              | Horizontal Offset             |

| 03H              | 83H             | VOS              | Vertical Offset               |

| 04H              | 84H             | DMM              | Display Memory Mode           |

| 05H              | 85H             | DMAH             | Display Memory Address High   |

| 06H              | 86H             | DMAL             | Display Memory Address Low    |

| 07H              | 87H             | DMDI             | Display Memory Data In        |

| 08H              | 88H             | CMM              | Character Memory Mode         |

| 09H              | 89H             | CMAH             | Character Memory Address High |

| 0AH              | 8AH             | CMAL             | Character Memory Address Low  |

| 0BH              | 8BH             | CMDI             | Character Memory Data In      |

| 0CH              | 8CH             | OSDM             | OSD Insertion Mux             |

| 10H              | 90H             | RB0              | Row 0 Brightness              |

| 11H              | 91H             | RB1              | Row 1 Brightness              |

| 12H              | 92H             | RB2              | Row 2 Brightness              |

| 13H              | 93H             | RB3              | Row 3 Brightness              |

| 14H              | 94H             | RB4              | Row 4 Brightness              |

| 15H              | 95H             | RB5              | Row 5 Brightness              |

| 16H              | 96H             | RB6              | Row 6 Brightness              |

| 17H              | 97H             | RB7              | Row 7 Brightness              |

| 18H              | 98H             | RB8              | Row 8 Brightness              |

| 19H              | 99H             | RB9              | Row 9 Brightness              |

| 1AH              | 9AH             | RB10             | Row 10 Brightness             |

| 1BH              | 9BH             | RB11             | Row 11 Brightness             |

| 1CH              | 9CH             | RB12             | Row 12 Brightness             |

| 1DH              | 9DH             | RB13             | Row 13 Brightness             |

| 1EH              | 9EH             | RB14             | Row 14 Brightness             |

| 1FH              | 9FH             | RB15             | Row 15 Brightness             |

| 6CH              | ECH             | OSDBL            | OSD Black Level               |

| _                | AxH             | STAT             | Status                        |

| _                | BxH             | DMDO             | Display Memory Data Out       |

| _                | CxH             | CMDO             | Character Memory Data Out     |

X = Don't care.

#### Video Mode 0 Register (VM0)

Write address = 00H, read address = 80H.

Read/write access: unrestricted.

To write to this register, the following conditions must be met:

- 1) STAT[5] = 0, the character memory (NVM) is not busy.

- 2) DMM[2] = 0, the display memory (SRAM) is not in the process of being cleared.

| BIT  | DEFAULT | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | 0       | Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6    | 0       | Video Standard Select<br>0 = NTSC<br>1 = PAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5, 4 | 00      | Sync Select Mode (Table 1)  0x = Autosync select (external sync when LOS = 0 and internal sync when LOS = 1)  10 = External  11 = Internal                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3    | 0       | Enable Display of OSD Image 0 = Off 1 = On                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2    | 0       | Vertical Synchronization of On-Screen Data  0 = Enable on-screen display immediately  1 = Enable on-screen display at the next VSYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1    | 0       | Software Reset Bit When this bit is set, all registers are set to their default values and the display memory is cleared. When a stable 27MHz clock is present, this bit is automatically cleared internally after typically 100µs. The user does not need to write a 0 afterwards. SPI operations should not be performed during this time or unpredictable results may occur. The status of the bit can be checked by reading this register after typically 100µs. This register is not accessible for writing until the display memory clear operation is finished (typically 20µs). |

| 0    | 0       | Video Buffer Enable 0 = Enable 1 = Disable (VOUT is high impedance)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

X = Don't care.

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

#### Video Mode 1 Register (VM1)

Write address = 01H, read address = 81H.

Read/write access: unrestricted.

| BIT     | DEFAULT | FUNCTION                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

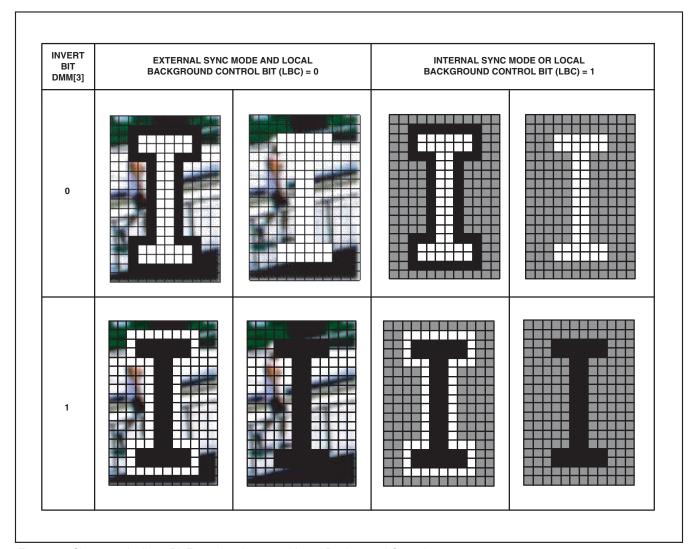

| 7       | 0       | Background Mode (See Table 4)  0 = The Local Background Control bit (see DMM[5] and DMDI[7]) sets the state of each character background.  1 = Sets all displayed background pixels to gray. The gray level is specified by bits VM1[6:4] below. This bit overrides the local background control bit.  Note: In internal sync mode, the background mode bit is set to 1. |  |

| 6, 5, 4 | 100     | Background Mode Brightness (% of OSD White Level)  000 = 0%  001 = 7%  010 = 14%  011 = 21%  100 = 28%  101 = 35%  110 = 42%  111 = 49%                                                                                                                                                                                                                                  |  |

| 3, 2    | 01      | Blinking Time (BT)  00 = 2 fields (33ms in NTSC mode, 40ms in PAL mode)  01 = 4 fields (67ms in NTSC mode, 80ms in PAL mode)  10 = 6 fields (100ms in NTSC mode, 120ms in PAL mode)  11 = 8 fields (133ms in NTSC mode, 160ms in PAL mode)                                                                                                                               |  |

| 1, 0    | 11      | Blinking Duty Cycle (On : Off)  00 = BT : BT  01 = BT : (2 x BT)  10 = BT : (3 x BT)  11 = (3 x BT) : BT                                                                                                                                                                                                                                                                 |  |

#### **Horizontal Offset Register (HOS)**

Write address = 02H, read address = 82H. Read/write access: unrestricted (Figure 23).

| BIT  | DEFAULT | FUNCTION                                                                                                                                                                                                   |

|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 6 | 00      | Don't Care                                                                                                                                                                                                 |

| 5–0  | 10 0000 | Horizontal Position Offset  (OSD video is not inserted into the horizontal blanking interval)  00 0000 = Farthest left (-32 pixels)  10 0000 = No horizontal offset  11 1111 = Farthest right (+31 pixels) |

#### **Vertical Offset Register (VOS)**

Write address = 03H, read address = 83H.

Read/write access: unrestricted (Figure 23).

| BIT     | DEFAULT | FUNCTION                                                                                                                                                                                            |

|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 6, 5 | 000     | Don't Care                                                                                                                                                                                          |

| 4–0     | 1 0000  | Vertical Position Offset (OSD video can be vertically shifted into the vertical blanking lines) 0 0000 = Farthest up (+16 pixels)  1 0000 = No vertical offset  1 1111 = Farthest down (-15 pixels) |

Figure 23. Character Display Area

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

Display Memory Mode Register (DMM)

Write address = 04H, read address = 84H.

Read/write access: unrestricted.

To write to this register, the following condition must be met:

$\mathsf{DMM}[2] = 0$ , the display memory is not in the process of being cleared.

| BIT | DEFAULT | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | 0       | Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6   | 0       | Operation Mode Selection  0 = 16-bit operation mode The 16-bit operation mode increases the speed at which the display memory can be updated. When writing to the display memory, the attribute byte is not entered through the SPI-compatible interface. It is entered automatically by copying DMM[5:3] to a character's attribute byte when a new character is written, thus reducing the number of SPI write operations per character from two to one (Figure 19). When in this mode, all characters written to the display memory have the same attribute byte. This mode is useful because successive characters commonly have the same attribute. This mode is distinct from the 8-bit operation mode where a character attribute byte must be written each time a character address byte is written to the display memory (see Table 5). When reading data from the display memory, both the Character Address byte and Character Attribute byte are transferred with the SPI-compatible interface (Figure 18). |

|     |         | The 8-bit operation mode provides maximum flexibility when writing characters to the display memory. This mode enables writing individual Character Attribute bytes for each character (see Table 5). When writing to the display memory, DMAH[1] = 0 directs the data to the Character Address byte and DMAH[1] = 1 directs the Character Attributes byte to the data. This mode is distinct from the 16-bit operation mode where the attribute bits are automatically copied from DMM[5:3] when a character is written.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5   | 0       | Local Background Control Bit, LBC (see Table 4)  Applies to characters written in 16-bit operating mode.  0 = Sets the background pixels of the character to the video input (VIN) when in external sync mode.  1 = Sets the background pixels of the character to the background mode brightness level defined by VM1[6:4] in external or internal sync mode.  Note: In internal sync mode, the local background control bit behaves as if it is set to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4   | 0       | Blink Bit, BLK Applies to characters written in 16-bit operating mode.  0 = Blinking off 1 = Blinking on  Note: Blinking rate and blinking duty cycle data in the Video Mode 1 (VM1) register are used for blinking control.  In external sync mode: when the character is not displayed, VIN is displayed.  In internal sync mode: when the character is not displayed, background mode brightness is displayed (see VM1[6:4]).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3   | 0       | Invert Bit, INV Applies to characters written in 16-bit operating mode (see Figure 24).  0 = Normal (white pixels display white, black pixels display black)  1 = Invert (white pixels display black, black pixels display white)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# Single-Channel Monochrome On-Screen Display with Integrated EEPROM

#### **Display Memory Mode Register (DMM) (continued)**

| BIT | DEFAULT | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2   | 0       | Clear Display Memory  0 = Inactive  1 = Clear (fill all display memories with zeros)  Note: This bit is automatically cleared after the operation is completed (the operation requires 20µs). The user does not need to write a 0 afterwards. The status of the bit can be checked by reading this register.  This operation is automatically performed:  a) On power-up  b) Immediately following the rising edge of RESET  c) Immediately following the rising edge of CS after VM0[1] has been set to 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 1   | 0       | Vertical Sync Clear  Valid only when clear display memory = 1, (DMM[2] = 1)  0 = Immediately applies the clear display-memory command, DMM[2] = 1  1 = Applies the clear display-memory command, DMM[2] = 1, at the next VSYNC time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |